Laporan Akhir 1

LAPORAN AKHIR 1

PERCOBAAN 1

1. Jurnal [kembali]

2. Alat dan Bahan[kembali]

- Panel DL 2203C.

- Panel DL 2203S.

- Jumper.

- Laptop.

- Software Proteus ver minimal 8.17

3. Rangkaian Simulasi [kembali]

Pada rangkaian diatas terdapat beberapa gerbang logika yang digunakan. Masing masing gerbang logika memiliki prinsip kerja yang berbeda.

- Gerbang NOT

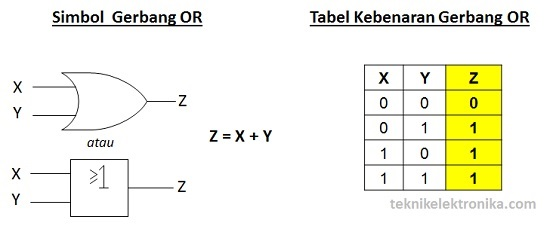

- Gerbang OR

A. Gerbang Logika

Praktikum percobaan gerbang logika ini menggunakan dua buah input utama, yaitu B0 dan B1. Kedua input tersebut kemudian dihubungkan ke beberapa rangkaian gerbang logika dasar, sehingga menghasilkan keluaran pada terminal H1 sampai dengan H7.

Setiap keluaran merepresentasikan jenis gerbang logika yang berbeda. H1 terhubung dengan gerbang NOT sehingga menghasilkan sinyal kebalikan dari input yang diberikan. H2 terhubung dengan gerbang AND, sehingga keluarannya bernilai logika 1 hanya jika kedua input bernilai 1. H3 terhubung dengan gerbang OR yang memberikan keluaran logika 1 apabila salah satu atau kedua input bernilai 1. H4 terhubung dengan gerbang XNOR yang menghasilkan keluaran logika 1 jika kedua input sama, baik sama-sama 0 maupun sama-sama 1. Pada jalur berikutnya, H5 kembali menggunakan AND, H6 menggunakan OR, dan H7 menggunakan XNOR sesuai dengan kombinasi jalur input yang dihubungkan.

Prinsip kerja dari percobaan ini adalah dengan memberikan kombinasi input B0 dan B1, yaitu 00, 01, 10, dan 11, kemudian mengamati perubahan keluaran pada setiap gerbang logika. Dengan cara ini, mahasiswa dapat memahami hubungan antara input dan output yang sesuai dengan tabel kebenaran masing-masing gerbang.

Rangkaian pertama menghasilkan keluaran H1. Input B0 dan D terlebih dahulu diproses oleh gerbang XNOR sehingga keluarannya akan bernilai 1 apabila kedua input memiliki nilai yang sama. Sementara itu, input A dan C diproses oleh gerbang AND yang hanya akan bernilai 1 apabila keduanya bernilai logika tinggi. Kedua hasil tersebut kemudian digabungkan melalui gerbang OR sehingga keluaran H1 akan bernilai logika 1 apabila salah satu kondisi terpenuhi, yaitu B0 sama dengan D atau A dan C sama-sama bernilai 1. Dengan demikian, persamaan logika dari rangkaian pertama dapat dituliskan sebagai H1 = (B0 XNOR D) + (A · C).

Rangkaian kedua menghasilkan keluaran H2. Sama seperti pada rangkaian H1, input B0 dan D diproses oleh gerbang XNOR untuk menghasilkan sinyal logika 1 jika keduanya sama. Perbedaannya terletak pada bagian bawah rangkaian, di mana input A, B, dan C diproses melalui gerbang AND tiga masukan. Hasil dari gerbang ini akan bernilai logika 1 hanya apabila ketiga input bernilai tinggi secara bersamaan. Kedua hasil kemudian digabungkan menggunakan gerbang OR sehingga keluaran H2 akan bernilai 1 apabila salah satu kondisi terpenuhi, yaitu B0 sama dengan D atau A, B, dan C semuanya bernilai 1. Persamaan logika dari rangkaian kedua dapat dituliskan sebagai H2 = (B0 XNOR D) + (A · B · C).

5. Video Rangkaian [kembali]

6. Analisa [kembali]

Percobaan 1 – Nomor 1

Soal:

Analisa masing-masing output h1 dan h2 ketika variasi input A, B, C, D pada percobaan 1b dengan persamaan:

-

-

.

Dari hasil analisa percobaan 1b, dapat disimpulkan bahwa output h1 dan h2 sangat bergantung pada kombinasi logika input A, B, C, dan D. Secara umum, keduanya sama-sama aktif (bernilai 1) ketika kondisi , sementara perbedaan utama terletak pada tambahan syarat logika: h1 dipengaruhi oleh kombinasi , sedangkan h2 dipengaruhi oleh kombinasi . Dengan demikian, meskipun keduanya sering bernilai sama pada kondisi tertentu, karakteristik persamaan membuat h1 lebih sensitif terhadap input C dan D, sementara h2 lebih sensitif terhadap input B dan C, sehingga pola keluaran tidak sepenuhnya identik.

Percobaan 2 – Nomor 1 (Encoder)

Soal:

Analisa pengaruh dari output low dan high pada percobaan encoder dengan input D0 sampai D9 dan output Y0 sampai Y3.

Percobaan encoder menunjukkan bahwa output dipengaruhi oleh jenis logika aktif yang digunakan. Pada encoder aktif high, input yang bernilai 1 langsung diterjemahkan ke kode biner pada output, sedangkan pada encoder aktif low, input yang bernilai 0 yang dipandang aktif dan menghasilkan output biner. Dengan demikian, perbedaan utama hanyalah pada polaritas logika, sementara fungsi utama encoder tetap sama, yaitu mengubah satu input yang aktif menjadi representasi biner pada output.

Percobaan 2 – Nomor 2 (Decoder IC 4028)

Soal:

Analisa setiap pengaruh input terhadap output decoder IC 4028 pada percobaan 2b, serta apa yang terjadi jika tidak ada input aktif dan jika input melebihi biner 9 (1001).

Pada percobaan decoder IC 4028, setiap kombinasi input BCD 0000 sampai 1001 menghasilkan satu output yang aktif (Y0 sampai Y9) sesuai angka desimalnya. Jika input berada pada kondisi 0000 maka output Y0 menyala, sedangkan jika input lebih besar dari 1001 maka tidak ada output valid yang aktif sehingga semua output tetap low atau berada pada kondisi tak terdefinisi. Hal ini menunjukkan bahwa IC 4028 memang dirancang khusus untuk penerjemahan BCD 0–9 ke keluaran desimal, sehingga penggunaannya terbatas hanya pada angka desimal valid.

Percobaan 3 – Nomor 1 (Multiplexer)

Soal:

Analisa hasil percobaan multiplexer ketika input data X0, X1, X2, X3 diberi variasi logika, lalu S0 dan S1 diubah-ubah.

Hasil percobaan multiplexer menunjukkan bahwa output hanya mengikuti salah satu input data sesuai kombinasi selektor S0 dan S1. Ketika S0S1=00, output menyalin X0; S0S1=01, output menyalin X1; S0S1=10, output menyalin X2; dan S0S1=11, output menyalin X3. Dengan demikian, variasi logika pada X0–X3 akan tampak di output tergantung jalur mana yang dipilih oleh selektor, membuktikan bahwa multiplexer bekerja sebagai pemilih data atau “saklar digital” dalam sistem logika.

Percobaan 3 – Nomor 2 (Demultiplexer)

Soal:

Analisa hubungan antara persamaan demultiplexer dengan persamaan decoder dan mengapa demultiplexer dianggap sebagai decoder yang diberi satu input data tambahan D.

Persamaan demultiplexer pada dasarnya merupakan persamaan decoder yang dikalikan dengan sinyal data D. Jika pada decoder keluaran hanya bergantung pada kombinasi selektor, maka pada demultiplexer keluaran yang aktif tidak hanya ditentukan selektor tetapi juga membawa nilai logika dari D. Hal ini membuktikan bahwa demultiplexer secara struktur identik dengan decoder, hanya berbeda pada adanya input tambahan berupa data. Karena itu, demultiplexer dapat dipandang sebagai decoder yang berfungsi untuk menyalurkan sinyal data ke jalur output yang dipilih.

7. Link Download [kembali]

- Rangkaian Proteus [Download]

- Video Percobaan 1a [Download]

- Video Percobaan 1b[Download]

- Data Sheet Gerbang NOT [Download]

- Data Sheet Gerbang OR [Download]

- Data Sheet Gerbang XOR [Download]

- Data Sheet Gerbang AND [Download]

- Data Sheet Gerbang NAND [Download]

- Data Sheet Gerbang XNOR [Download]

Comments

Post a Comment